DDR系列内存详解及硬件设计规范-希望对您有帮助

”DDR 硬件设计规范“ 的搜索结果

飞思卡尔 DDR硬件设计规范

标签: DDR

标准的DDR2硬件设计规范,飞思卡尔的检查单,对于单板的DDR设计有指导意义,非常有用

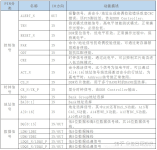

DDR2、DDR3、DDR4、DDR5规范,此外还有测试指导、layout指导,硬件设计指导

DDR2应用设计规范

标签: 硬件 DDR2

DDR2应用设计规范,不错的一份文档,在DDR2设计中有指导性作用。

二、走线拓扑所有信号组,除了数据组外,全部用Fly by结构3、端接匹配端接电阻摆放在末端。时钟comp电容摆放在源端。4、等长原则注意:①.DQSP和DQSN要在同一层进行布线,DQSP/DQSN差分...实际设计时参考datasheet。6、

包括DDR2、DDR3、DDR4、DDR5规范,此外还有测试指导、layout指导,硬件设计指导。

DDR4-DRAM是第四代支持双倍数据读取,支持随机位置存取的静态存储器。DDR4-DRAM的工作原理。...DDR的硬件设计。DDR4 PCB设计要点介绍。DDR4之PCB走线间距的串扰评估。DDR4之内存通道(channel)和内存列(rank)。

ddr设计规范参考

标签: DDR2 PCB设计

DDR2相关设计规范,本规范对终端电阻处理,以及等长处理进行相关地说明,对于硬件从业人员有一定的指导意义。

DDR3的设计规范,,可以供硬件工程师开发的时候以及研发的时候参考用

XILINX SPARTAN3A DDR2接口设计应用文档,有连接,电源,时钟的设计参考

全志 A64 全套硬件开发资料SDK开发包说明文档硬件设计说明DDR Layout模板等资料 IC资料包 SDK开发包说明文档 硬件发布资料包 a64 3G Dongle Support List.pdf A64 Camera模块开发说明文档.pdf A64 Camera自适应使用...

硬件设计之二——信号设计01:DDR设计 在目前的处理器架构中,DDR是必不可少的一部分。毫无疑问,DDR部分是系统高速信号中最重要的部分。 本文分为2部分,一部分是对于信号处理的规则,另一部分是一些注意事项。 ...

一、硬件设计原则: 1. 所有的设计依据来自于元器件SPEC,必须详细阅读各个元件的规格书并深入理解; 2. &nb...

DDR硬件调试篇前言:大家自己设计的产品出来后都有遇到一些什么样的DDR问题呢?这些问题是否为致命问题,一定要解吗?如果机器已经生产出来,却发现DDR硬件问题导致系统不稳定,机器是否作废了,有没有软件方法可以...

硬件设计-DDR4内存条设计

DDR内存的电源设计非常重要,以下是一些DDR硬件设计的要点: 1. 电源噪声控制:DDR内存对电源噪声非常敏感,因此需要在设计中采用合适的电源滤波器以控制电源噪声。此外,电源和地线的布线也需要遵循规范,以最小化...

DDR3特点和设计指导.pdf

标签: ddr

本文描述DDR3特点和设计指导。讲解高速电路的设计和走线规范,值得硬件朋友的参考。高速走线设计要求非常高,需要的朋友可以下载。谢谢

DDR3电路设计

DDR3的设计规范,,可以供硬件工程师开发的时候以及研发的时候参考用 相关下载链接://download.csdn.net/download/nsxpyt/9011045?utm_source=bbsseo

推荐文章

- Ubuntu/linux下下载工具_ubuntu下载软件助手 linux版本-程序员宅基地

- HTML、JSP前端页面国际化(i18n)_html全局国际化-程序员宅基地

- Python高级-08-正则表达式_写出能够匹配只有下划线和数字还有字母组成(且第一个字符必须为字母)的163邮箱(@1-程序员宅基地

- 寻仙手游维护公告服务器停服更新,寻仙手游2月1日停服更新公告 2月1日更新了什么...-程序员宅基地

- 用python自动预约图书馆座位_微信图书馆座位秒抢脚本-程序员宅基地

- Android真机或模拟器激活Xposed框架的方法_de.robv.android.xposed.installer-程序员宅基地

- 操作系统为什么要分用户态和内核态_用户态和内核态都需要cpu参与,为什么要区分-程序员宅基地

- 01—JVM与Java体系结构(简单介绍)_01_jvm与java体系结构.pptx-程序员宅基地

- 国有建筑企业数字化转型整体解决方案_建筑企业数字化转型行动方案-程序员宅基地

- 性能测试的软件------loadrunner_loadrunner有有三个图标,-程序员宅基地